DIP аңлау

DIP - плагин. Бу рәвешчә пакетланган чипларның ике рәт кадаклары бар, алар турыдан-туры DIP структурасы булган чип розеткаларына эретеп яисә шул ук санлы тишекләр белән эретеп ябыштыру урыннарына эретеп була. PCB такта перфорациясен эретеп ябыштыруны тормышка ашыру бик уңайлы, һәм ана тактасы белән яхшы яраклаша, ләкин аның төрү мәйданы һәм калынлыгы чагыштырмача зур булганга, кертү һәм чыгару процессындагы пинны бозу җиңел, ышанычлылыгы начар.

DIP - иң популяр плагин пакеты, кушымта диапазонына стандарт логик IC, хәтер LSI, микрокомпьютер схемалары һ.б. керә, кечкенә профиль пакеты (SOP), SOJ (J тибындагы кечкенә профиль пакеты), TSOP (нечкә кечкенә профиль пакеты), VSOP (бик кечкенә профиль пакеты), SSOP (кыскартылган SOP), TSSOP (кечерәйтелгән SOP) һәм SOT (кечкенә профиль транспорты)

DIP җайланма җыю дизайны җитешсезлеге

PCB пакет тишеге җайланмадан зуррак

PCB плагин тишекләре һәм пакет пин тишекләре спецификацияләр нигезендә сызылган. Тәлинкә ясау вакытында тишекләрдә бакыр каплау кирәклеге аркасында, гомуми толерантлык плюс яки минус 0,075 мм. PCB төрү тишеге физик җайланманың кадакыннан артык зур булса, бу җайланманың йомшаруына, калайның җитмәвенә, һава эретеп ябыштыруга һәм башка сыйфат проблемаларына китерәчәк.

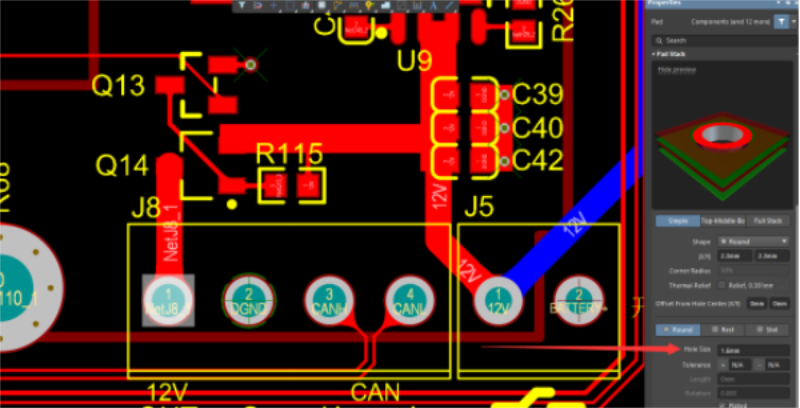

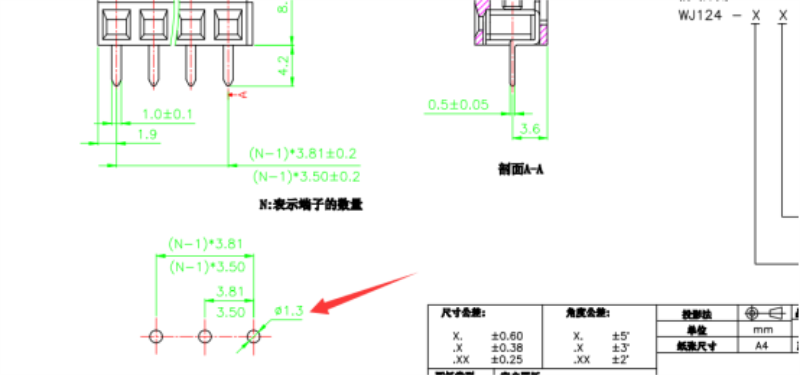

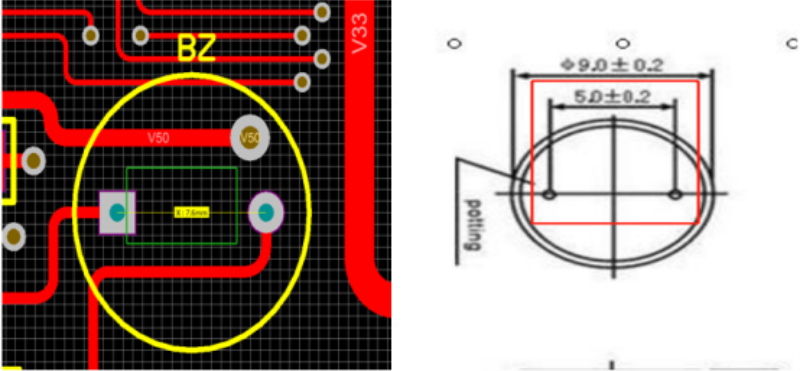

WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) җайланмасы пины 1,3 мм, PCB төрү тишеге 1,6 мм, держава дулкын эретеп эретү вакытын эретеп ябыштыруга китерә.

Фигурага бәйләнгән, дизайн таләпләре буенча WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) компонентларын сатып алыгыз, 1,3 мм кадак дөрес.

PCB пакет тишеге җайланмадан кечерәк

Плагин, ләкин бакыр тишмәячәк, әгәр ул бер һәм ике панель бу ысулны куллана алса, бер һәм ике панель тышкы электр үткәргеч, эретеп үткәргеч булырга мөмкин; Күпкатлы тактадагы плагин тишеге кечкенә, һәм PCB такта эчке катламда электр үткәргеч булганда гына төзәтеп була, чөнки эчке катлам үткәрүне реаминг белән төзәтеп булмый.

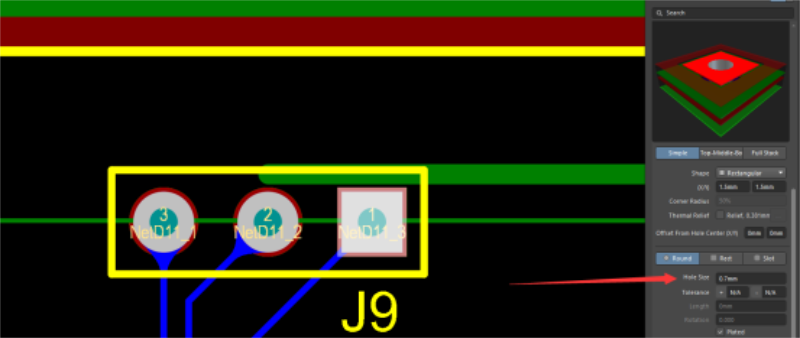

Түбәндәге рәсемдә күрсәтелгәнчә, A2541Hwv-3P_A2541HWV-3P (CJT) компонентлары дизайн таләпләре буенча сатып алына. Пин 1,0 мм, һәм PCB мөһер тактасы тишеге 0,7 мм, нәтиҗәдә кертү уңышсызлыкка китерә.

A2541Hwv-3P_A2541HWV-3P (CJT) компонентлары дизайн таләпләренә туры китереп сатып алына. 1,0 мм кадак дөрес.

Пакет пин арасы җайланма арасыннан аерылып тора

DIP җайланмасының PCB мөһерләү тактасы пин белән бер үк державага гына түгел, ә тишек тишекләре арасына бер үк ара кирәк. Әгәр тишек тишекләре белән җайланма арасы туры килмәсә, җайланма урнаштырыла алмый, көйләнә торган аяк арасы булган өлешләрдән кала.

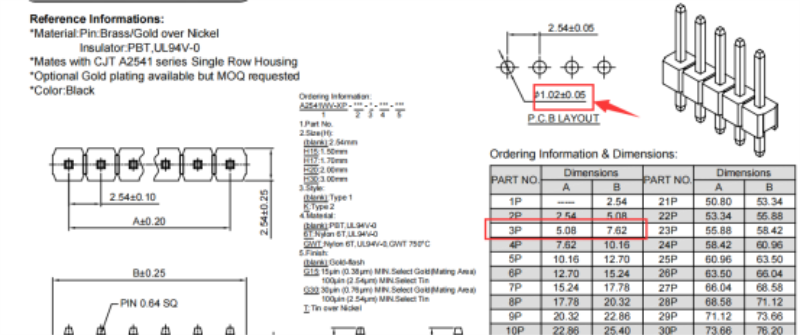

Түбәндәге рәсемдә күрсәтелгәнчә, PCB упаковкасының тишек арасы 7,6 мм, сатып алынган компонентларның тишек арасы 5,0 мм. 2.6 мм аермасы җайланманың кулланылмавына китерә.

PCB төрү тишекләре бик якын

PCB дизайнында, рәсем ясауда һәм төрүдә, тишекләр арасына игътибар итергә кирәк. Ялан тәлинкә барлыкка килсә дә, тишек тишекләре арасы кечкенә, дулкын эретеп монтаж вакытында калай кыска схемага китерү җиңел.

Түбәндәге рәсемдә күрсәтелгәнчә, кыска схема кечкенә пин арасы аркасында булырга мөмкин. Калайны эретүдә кыска схеманың күп сәбәпләре бар. Дизайн ахырында җыюны алдан кисәтеп була икән, проблемалар очраклары кимергә мөмкин.

DIP җайланмасы проблемасы

Проблеманы тасвирлау

DIP продуктының дулкын кресты белән эретеп ябыштырганнан соң, челтәр эретеп ябыштыручы челтәр розеткасының эретелгән тәлинкәсендә калай җитмәве ачыкланды.

Проблема йогынтысы

Нәтиҗәдә, челтәр розеткасының һәм PCB такта тотрыклылыгы начарлана, һәм сигнал пин аяк көче продуктны кулланганда кулланылачак, бу ахыр чиктә сигнал пинның тоташуына китерәчәк, продукт эшенә тәэсир итәчәк һәм кулланучылар куллануда уңышсызлык куркынычына китерәчәк.

Проблеманы киңәйтү

Челтәр розеткасының тотрыклылыгы начар, сигнал пинның тоташу эше начар, сыйфат проблемалары бар, шуңа күрә ул кулланучыга куркынычсызлык китерергә мөмкин, соңгы югалту күз алдына да китереп булмый.

DIP җайланмаларын җыю анализы

DIP җайланмасы кадаклары белән бәйле күп проблемалар бар, һәм бик күп төп пунктларны игътибарсыз калдыру җиңел, нәтиҗәдә соңгы такталар. Алайса, мондый проблемаларны ничек тиз һәм тулысынча чишәргә?

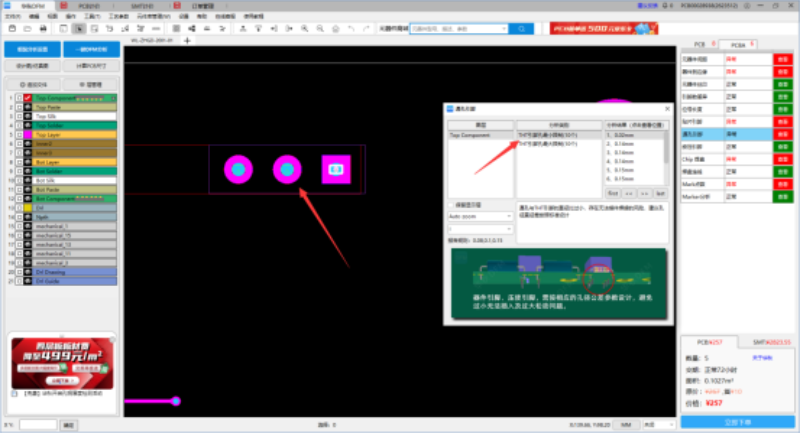

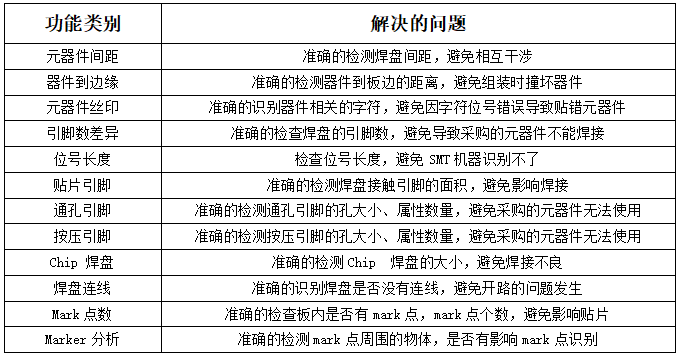

Монда, безнең CHIPSTOCK.TOP программа тәэминаты җыю һәм анализлау функциясе DIP җайланмалары кадакларында махсус тикшерү үткәрү өчен кулланылырга мөмкин. Тикшерү пунктларына тишекләр аша кадаклар саны, THT кадакларының зур чиге, THT кадакларының кечкенә чикләре һәм THT кадакларының атрибутлары керә. Пинкларны тикшерү әйберләре, нигездә, DIP җайланмалары дизайнында булган проблемаларны каплый.

PCB дизайны тәмамланганнан соң, PCBA җыю анализы функциясе алдан дизайн җитешсезлекләрен ачыклау, производство алдыннан дизайн аномалияләрен чишү, монтажлау процессында проект проблемаларыннан саклану, җитештерү вакытын тоткарлау, калдыкларны тикшерү һәм үсеш чыгымнары.

Аның җыю анализы функциясендә 10 төп әйбер һәм 234 яхшы әйберне тикшерү кагыйдәләре бар, алар монтажлау проблемаларын үз эченә ала, мәсәлән, җайланма анализы, пин анализы, такта анализы һ.б., алар инженерлар алдан көтә алмаган төрле җитештерү ситуацияләрен чишә ала.

Пост вакыты: Июль-05-2023